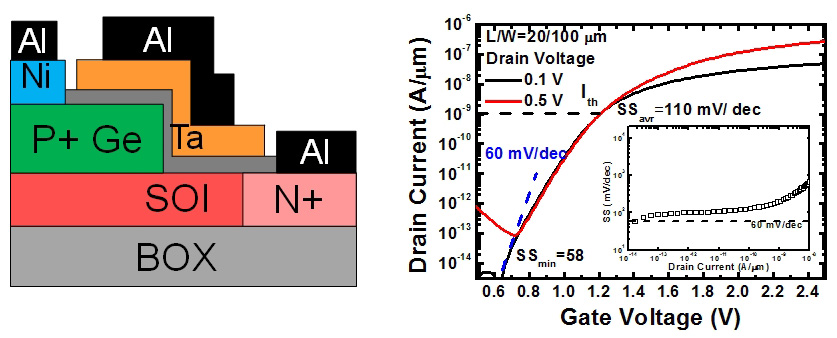

Ge MOSFET

次世代高性能MOSFETとして期待されるGe MOSFETの研究を行っています。

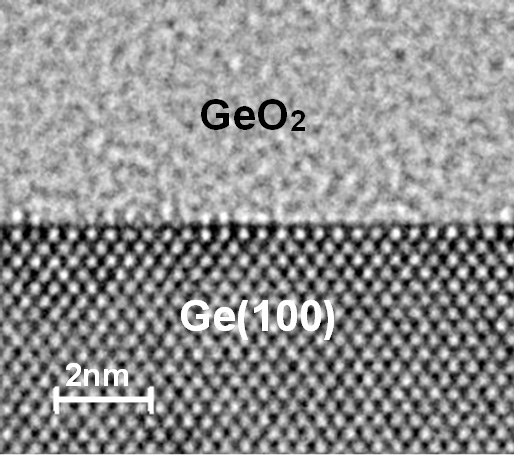

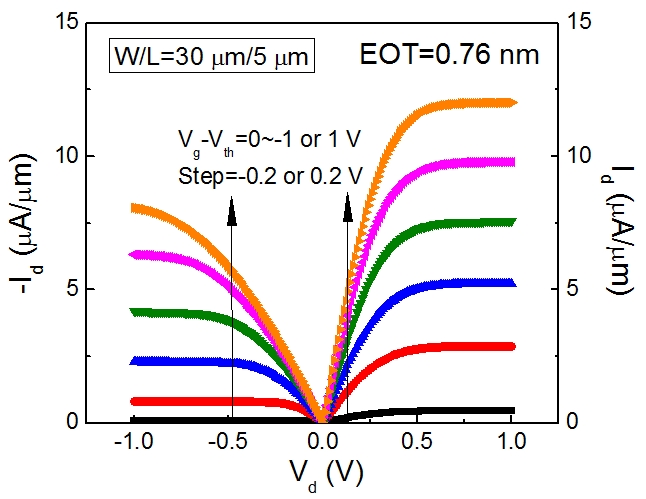

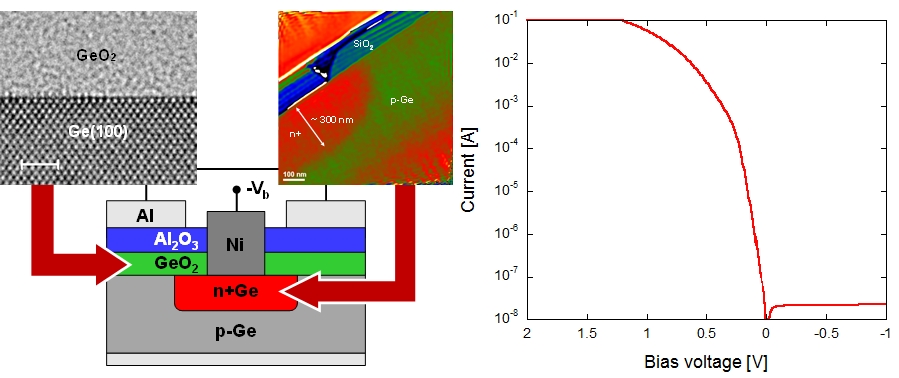

我々は、清浄な環境下でGeを高温熱酸化することで、極めて界面欠陥の少ない良好なGeO2/Ge MOS界面の形成に成功しました[1] 。1011cm-2eV-1程度の低界面準位密度を実現しており、従来のSiに対して3倍程度の移動度をもつGe pMOSFETを実現しています[2]。また、気相ドーピング技術を用いて形成したn+S/Dを利用した高性能Ge nMOSFETの動作にも成功し、Siを上回る性能を実証しています[3]。さらに、プラズマ酸化法を用いて、等価換算膜厚0.76nmの極薄ゲート絶縁膜MOSFETの作製にも成功するなど、Ge CMOS実現に向けた研究を進めています[4-7]。

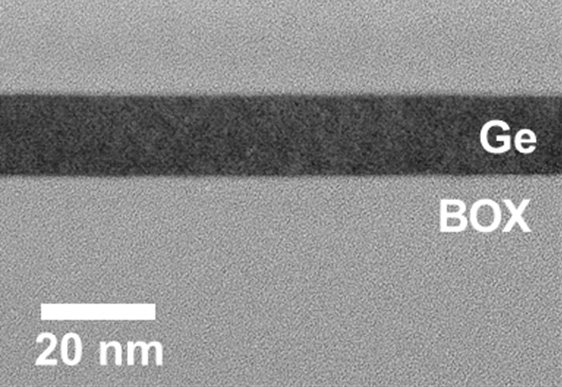

酸化濃縮法やウェハボンディングを用いることで、Si基板上にGe層やSiGe層を形成する研究も進めています。これまでに、酸化濃縮でGe-on-Insulator基板を作製し、良好なトランジスタ動作を実証することに成功しています[8-10]。

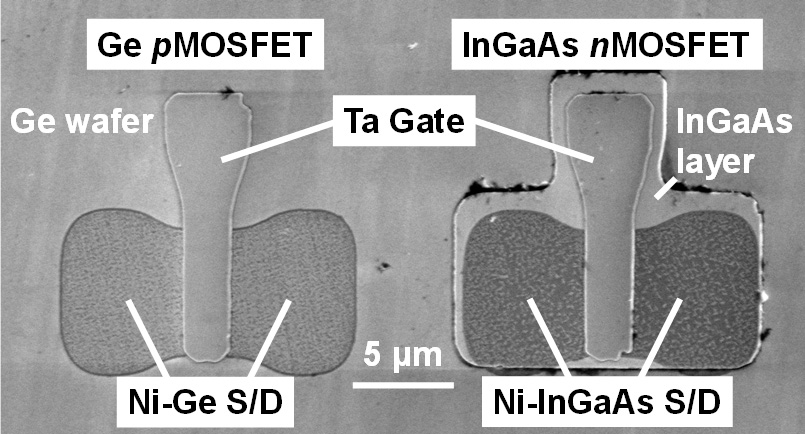

また、ウェハボンディングによりIII-V MOSFETとGe MOSFETを一体集積したIII-V/Ge CMOS構造を世界で初めて実証することに成功しました[11]。

TEM image of

GeO2/Ge MOS interface

Output characteristics of Ge CMOS formed by plasma post oxidation

Ge condensation by thermal oxidation

III-V/Ge CMOS

[1] H. Matsubara, T. Sasada, M. Takenaka and S. Takagi, Appl. Phys. Lett., Vol. 93, 032104, 2008.

[2] Y. Nakakita, R. Nakane, T. Sasada, H. Matsubara, M. Takenaka and S. Takagi, International Electron Devices Meeting (IEDM’08), 35-6, San Francisco, December 2008.

[3] K. Morii, T. Iwasaki, R. Nakane, M. Takenaka, and S. Takagi, International Electron Devices Meeting (IEDM’09), 29.3, Baltimore, December 2009.

[4] R. Zhang, N. Taoka, P. Huang, M. Takenaka, S. Takagi, International Electron Devices Meeting (IEDM’11), 28.3, Washington D.C., December 2011.

[5] R. Zhang, P.C. Huang, J.C. Lin, M. Takenaka, S. Takagi, International Electron Devices Meeting (IEDM’12), 16.1, San Francisco, December 2012.

[6] R. Zhang, W. Chern, X. Yu, M. Takenaka, J. L. Hoyt, S. Takagi, " High mobility strained-Ge pMOSFETs with 0.7-nm ultrathin EOT using plasma post oxidation HfO2/Al2O3/GeOx gate stacks and strain modulation," International Electron Devices Meeting (IEDM’13), 26.1, Washington D. C., 11 December 2013.

[7] R. Zhang, X. Yu, M. Takenaka, and Shinichi Takagi, “Impact of channel orientation on electrical properties of Ge p- and n-MOSFETs with 1-nm EOT Al2O3/GeOx/Ge gate stacks fabricated by plasma post oxidation,” IEEE Trans. Electron Devices, vol. 61, no. 11, pp. 3668 – 3675, 2014.

[8] S. Dissanayake, Y. Zhao, S. Sugahara, M. Takenaka, and S. Takagi, J. Appl. Phys., vol. 109, 033709, 2011.

[9] J. Suh, R. Nakane, N. Taoka, M. Takenaka, and S. Takagi, Appl. Phys. Lett., Vol. 99, 142108, 2011.

[10] W. Kim, K. Kuroda, M. Takenaka, and S. Takagi, “Sb-doped S/D ultra-thin body Ge-on insulator nMOSFET fabricated by improved Ge condensation process,” IEEE Trans. Electron Devices, vol. 61, no. 10, pp. 3379 – 3385, 2014.

[11] M. Yokoyama, S. Kim, R. Zhang, N. Taoka, Y. Urabe, T. Maeda, H. Takagi, T. Yasuda, H. Yamada, O. Ichikawa, N. Fukuhara, M. Hata, M. Sugiyama, Y. Nakano, M. Takenaka, and S. Takagi, “III–V/Ge high mobility channel integration of InGaAs n-channel and Ge p-channel metal–oxide–semiconductor field-effect transistors with self-aligned Ni-based metal source/drain using direct wafer bonding,” Appl. Phys. Express., Vol. 5, 076501, 2012.

III-V MOSFET

極めて大きな電子移動度をもつIII-V族半導体を用いた次世代高性能n-MOSFETを実現するための研究を行っています。

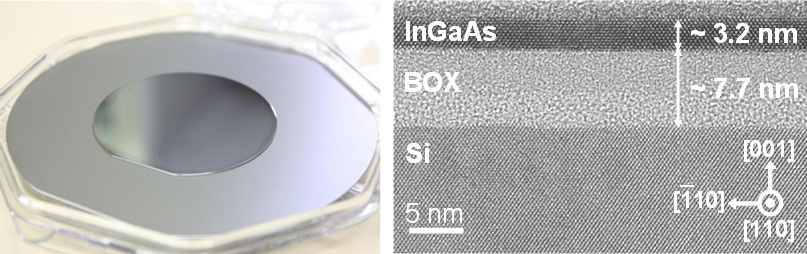

既存のSiプラットフォームにIII-V族半導体を集積するために、ダイレクトウェハーボンディング技術の研究を進めています[1-2]。これまでに、3nmの極薄InGaAs層をSi基板に貼り合わせたIII-V-on-Insulator (III-V-OI) on Si基板を作製し、良好なトランジスタ動作を得ることに成功しています[3]。

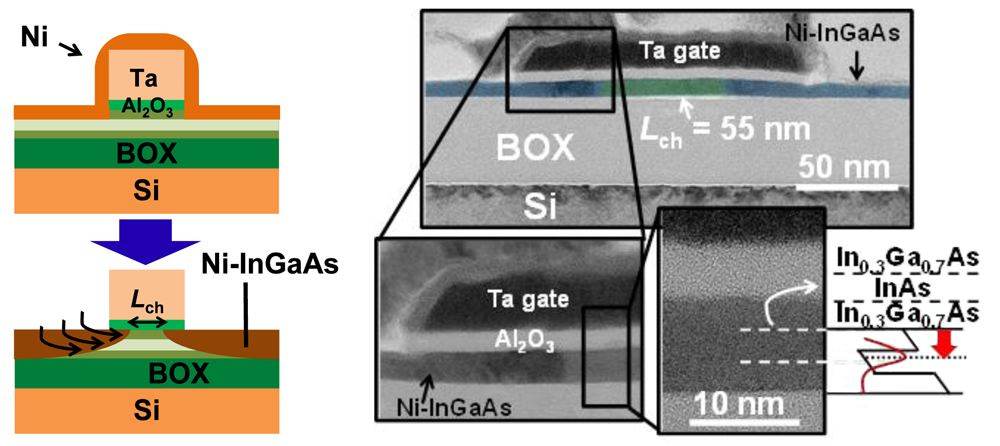

既存のイオン注入法に代わり、低抵抗ソース/ドレインを低温で形成可能なメタルソース/ドレインの研究も進めています[4-5]。我々は、Ni-InGaAs合金を用いて自己整合メタルソース/ドレインの作製に世界で初めて成功しています。これまでに、Si基板上に貼り合わせたIII-V-OI基板を用いて、ゲート長55nmのトランジスタ動作に成功しています[6]。さらにゲート長20nmの立体ゲートInGaAsトランジスタの実証にも成功しています[7]。

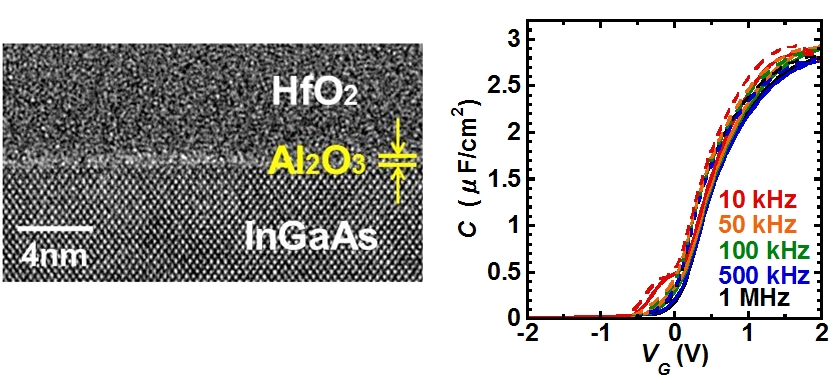

原子層堆積法(ALD)を用いて良好なInGaAs MOS界面を形成する研究も進めている。高誘電率絶縁膜であるHfO2においては、MOS界面特性が堆積温度に大きく依存し、200度で堆積したときに最も良好な界面特性が得られることを明らかにしました[8]。またHfO2とInGaAsの間にAl2O3界面層を2サイクル挿入することで、良好な界面特性を維持したままCETを1.08 nmまでスケーリングすることに成功しました[9]。さらにInGaAs MOS界面においては、伝導体内における界面準位がトランジスタ特性に大きく影響することをホール測定とC-V測定から明らかにしました[10]。

III-V-on-insulator wafer bonded on Si

Self-align Ni-InGaAs metal S/D for Ni-InGaAs MOSFETs

TEM image and C-V characteristic of HfO2/Al2O3/InGaAs MOS capacitor with CET of 1.08 nm

[1] M. Yokoyama, T. Yasuda, H. Takagi, H. Yamada, N. Fukuhara, M. Hata, M. Sugiyama, Y. Nakano, M. Takenaka, and S. Takagi, VLSI Symposium., 12B-3, Kyoto, June 2009.

[2] M. Yokoyama, T. Yasuda, H. Takagi, H. Yamada, N. Fukuhara, M. Hata, M. Sugiyama, Y. Nakano, M. Takenaka, S. Takagi, Appl. Phys. Express., Vol. 2, 124501, 2009.

[3] M. Yokoyama, R. Iida, S. H. Kim, N. Taoka, Y. Urabe, T. Yasuda, H. Takagi, H. Yamada, N. Fukuhara, M. Hata, M. Sugiyama, Y. Nakano, M. Takenaka, and S. Takagi, International Electron Devices Meeting (IEDM’10), 3.1, San Francisco, December 2010.

[4] S.H. Kim, M. Yokoyama, N. Taoka, R. Iida, S. Lee, R. Nakane, Y. Urabe, N. Miyata, T. Yasuda, H. Yamada, N. Fukuhara, M. Hata, M. Takenaka, S. Takagi, International Electron Devices Meeting (IEDM’10), 26.6, San Francisco, December 2010.

[5] S.H. Kim, M. Yokoyama, N. Taoka, R. Nakane, T. Yasuda, M. Ichikawa, N. Fukuhara, M. Hata, M. Takenaka, S. Takagi, International Electron Devices Meeting (IEDM’11), 13.4, Washington D.C., December 2011.

[6] S. H. Kim, M. Yokoyama, N. Taoka, R. Nakane, T. Yasuda, O. Ichikawa, N. Fukuhara, M. Hata, M. Takenaka, S. Takagi, VLSI Symposium., 21.1, Honolulu, June 2012.

[7] S. H. Kim, M. Yokoyama, R. Nakane, M. Ichikawa, T. Osada, M. Hata, M. Takenaka, S. Takagi, "High performance sub-20-nm-channel-length extremely-thin body InAs-on-Insulator tri-gate MOSFETs with high short channel effect immunity and Vth tunability," International Electron Devices Meeting (IEDM’13), 16.4, Washington D. C., 10 December 2013.

[8] R. Suzuki, Noriyuki Taoka,M. Yokoyama,S.H. Kim, T. Hoshii,T. Maeda,T. Yasuda,O. Ichikawa, N. Fukuhara, M. Hata, M. Takenaka, and S. Takagi, J. Appl. Phys., vol. 112, 084103, 2012.

[9] R. Suzuki, N. Taoka, M. Yokoyama, S. Lee, S. H. Kim, T. Hoshii, T. Yasuda, W. Jevasuwan, T. Maeda, O. Ichikawa, N. Fukuhara, M. Hata, M. Takenaka, and S. Takagi, Appl. Phys. Lett., Vol. 100, 132906, 2012.

[10] N. Taoka, M. Yokoyama, S.H. Kim, R. Suzuki, R. Iida, S. Lee, T. Hoshii, W. Jevasuwan, T. Maeda, T. Yasuda, O. Ichikawa, N. Fukuhara, M. Hata, M. Takenaka, and S. Takagi, International Electron Devices Meeting (IEDM’11), 27.2, Washington D.C., December 2011.

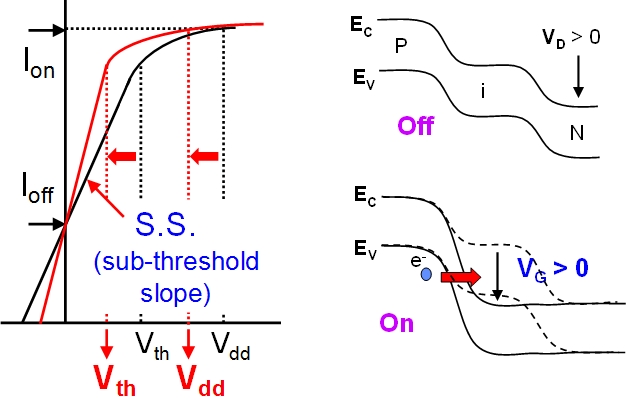

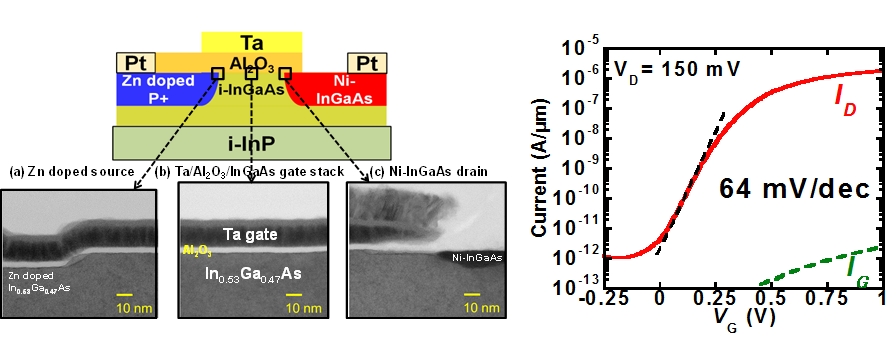

量子トンネルFET

MOSFETのオン・オフの立ち上がりの鋭さを表すサブスレショルドスロープは物理的に60 mV/dec.以下にならないことが知られています。このため、電源電圧をスケーリングに伴い下げることが年々困難になってきており、LSIの消費電力を下げるうえで大きな問題となっています。このため、量子トンネル効果を用いた新原理トランジスタの研究が世界的に活発になってます。量子トンネル効果を持ちることで、サブスレショルドスロープが60 mV/dec.以下の急峻なトランジスタが可能になり、LSIの消費電力を大幅に削減できるものと期待されています。

我々は、Siよりも急峻なサブスレショルドスロープが得られることが期待されているInGaAsを用いたトンネルFETの研究に取り組んでいます。これまでに横方向PIN構造を用いたInGaAs トンネル FET動作に成功しています[1,2]。またSOGからのZn拡散を用いることで、極めて急峻な接合を形成することで、世界最高レベルの性能をもつInGaAs トンネルFETの動作実証に成功し[3]、さらなる高性能を目指した研究を進めています。

Ge/SiトンネルFETの研究にも取り組んでいます。SOIや歪SOI基板上にGeソースを成長することで、高性能トンネルFET動作の実証に成功しています [4-6]。

Operation principle of Tunnel FET

InGaAs tunnel FET

Ge/Si tunnel FET

[1] R. Iida, S. H. Kim, M. Yokoyama, N. Taoka, S. H. Lee, M. Takenaka, and S. Takagi, J. Appl. Phys., vol. 110, 124505, 2011.

[2] R. Iida, S. H. Kim, M. Yokoyama, N. Taoka, S. H. Lee, M. Takenaka and S. Takagi, International Conference on Solid State Devices and Materials (SSDM’11), D-4-1, Nagoya, September 2011.

[3] M. Noguchi, S. Kim, M. Yokoyama, O.Ichikawa, T. Osada, M. Hata, M. Takenaka, S. Takagi, International Electron Devices Meeting (IEDM’13), 28.1, Washington D. C., 11 December 2013.

[4] M. Kim, Y. Wakabayashi, R. Nakane, M. Yokoyama, M. Takenaka and S. Takagi, International Electron Devices Meeting (IEDM’14), 13.2, San Francisco, 16 December 2014.

[5] M. Kim, Y. Kim, M. Yokoyama, R. Nakane, S.-H. Kim, M. Takenaka, and S. Takagi, Thin Solid Films, Vol. 557, pp. 298-301, 2014.

[6] M. Kim, Y. Ki. Wakabayashi, M. Yokoyama, R. Nakane, M. Takenaka, and Shinichi Takagi, IEEE Trans. Electron Devices, vol. 62, no. 1, pp. 9 – 15, 2015.

光配線LSI

ムーアの法則に従ったスケーリング則により大規模集積回路(LSI)中のトランジスタの高性能化は進んでいる一方、配線部分での消費電力や信号遅延増加がより深刻な問題となっています。LSIの消費電力の約50%が配線部分での発熱になっていると言われており、LSIの性能向上の妨げとなっています。我々は、Siフォトニクス技術を用いて、LSI配線の一部を光配線に置き変えるオンチップ光配線や光入出力付きLSIを実現するオフチップ光配線の研究を進めています。Siフォトニクスは、高度なCMOS製造技術を用いることで、 Si-on-Insulator基板上に大規模光集積回路を実現する技術であり、大規模光集積回路の主流プラットフォームとして世界中で活発に研究を進められています。CMOS回路の集積化も可能であり、今後、光通信用光集積回路はSiフォトニクスが主流になると期待されています。我々の研究室では、 光配線LSI等を実現するために、SiGeやGe,III-V族半導体などの新しい材料を導入したSiフォトニクスなどの研究を進めています。

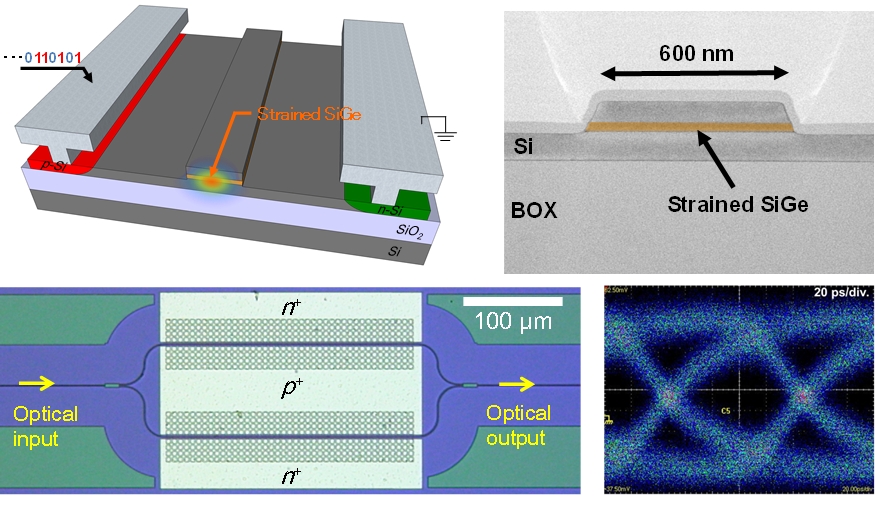

歪みSiGe光変調器

電気信号を光信号に変換するSi光変調器はSiフォトニクスにおいて重要な素子である一方、変調効率がよくないことが課題となっています。我々は、有効質量の軽い半導体により変調効率を改善する有効質量エンジニアリングを提唱し、Si光変調器の高性能化を目指しています[1]。ホールの有効質量が軽い半導体として歪みSiGeを用いた歪SiGe光変調器の研究を進めています。これまでにキャリア注入型歪SiGe光変調器の動作に成功し、プラズマ分散効果や自由キャリア吸収の増大を実証しています[2-4]。またマッハ・ツェンダー干渉型変調器において10Gbpsでの変調動作にも成功しています[5]。SiGeは既にLSI中のトランジスタとして用いられており、CMOSファブでの取り扱いが容易であるという利点があります。これを活かして、現在実用化に向けた研究を進めています[6]。

Strained SiGe optical modualtor

[1] M. Takenaka and S. Takagi, IEEE J. Quantum Electron., vol. 48, no. 1, pp. 8 - 15, 2012.

[2] Y. Kim, M. Takenaka, T. Osada, M. Hata, S. Takagi, "Strain-induced enhancement of free-carrier effects in SiGe for optical modulator and VOA applications," Optical Fiber Communication Conference (OFC2014), Th1C.4, San Francisco, 13 March 2014.

[3] Y. Kim, M. Takenaka, T. Osada, M. Hata, and S. Takagi, “Strain-induced enhancement of plasma dispersion effect and free-carrier absorption in SiGe optical modulators”, Scientific Reports, vol. 4, 4683, 2014.

[4] Y. Kim, J. Fujikata, S. Takahashi, M. Takenaka, and S. Takagi, "Record-low injection-current strained SiGe variable optical attenuator with optimized lateral PIN junction," European Conference on Optical Communication (ECOC’14), Cannes, P.2.6, 24 September 2014.

[5] Y. Kim, J. Fujikata, S. Takahashi, M. Takenaka, and S. Takagi, "SiGe-based carrier-injection Mach-Zehnder modulator with enhanced plasma dispersion effect in strained SiGe," Optical Fiber Communication Conference (OFC2015), Tu2A.7, Los Angeles, 24 March 2015.

[6] J. Fujikata, M. Noguchi, J. Han, S. Takahashi, M. Takenaka, and T. Nakamura, “Record-high Modulation-efficiency Depletion-type Si-based optical modulator with in-situ B doped strained SiGe layer on Si waveguide for 1.3 um wavelength,” European Conference on Optical Communication (ECOC 2016), Düsseldorf, Tu3.A.4, 20 September 2016.

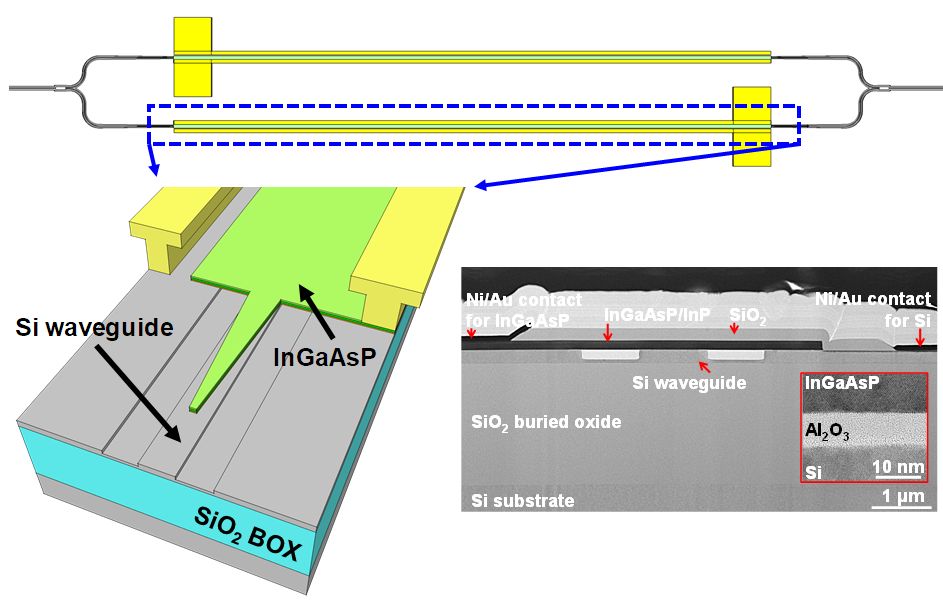

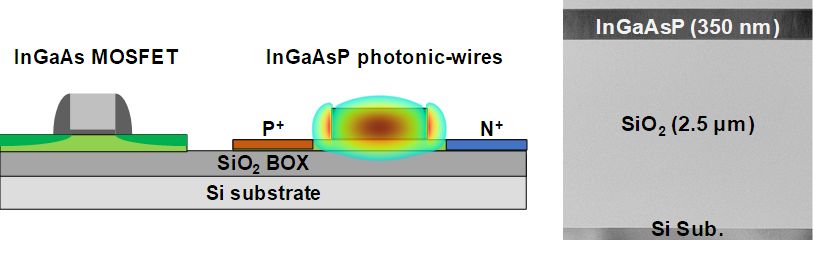

III-V/SiハイブリッドMOS型光変調器

電子の有効質量が軽いIII-V族半導体であるInGaAsPをSi導波路上に貼り合わせたハイブリッドMOS型光変調器を世界に先駆けて提唱し、研究を進めています[1-4]。ゲート絶縁膜となるアルミナを介してInGaAsPを貼り合わせることで、InGaAsP MOS界面での電子蓄積により光変調することに世界で初めて成功しました。InGaAsP中の電子誘起屈折率変調を用いることで、0.047 Vcmと極めて高い位相変調効率を実現しました。これは半導体光変調器として最も効率の高い値であり、既存のSi変調器の性能を大幅に上回るものです。変調時光損失もSi光変調器の約1/10に低減することに成功し、高効率・低損失・高速光変調器の実現が期待され、100 Gbpsを超える次世代光通信用変調器の実現に向けた研究を進めています。

III-V/Si hybrid MOS optical modulator

[1] J.-H. Han, F. Boeuf, J. Fujikata, S. Takahashi, S. Takagi, and M. Takenaka, “Efficient low-loss InGaAsP/Si hybrid MOS optical modulator,” Nature Photonics, vol. 11, no. 8, pp. 486–490, Jul. 2017.

[2] J. Han, M. Takenaka, and S. Takagi, “Extremely high modulation efficiency III-V/Si hybrid MOS optical modulator fabricated by direct wafer bonding,” International Electron Devices Meeting (IEDM’16), 25.5, San Francisco, 7 December 2016.

[3] J. Han, S. Takagi, and M. Takenaka, “High-Efficiency O-Band Mach-Zehnder modulator based on InGaAsP/Si hybrid MOS capacitor,” Optical Fiber Communication Conference (OFC2017), W3E.2, Los Angeles, 22 March 2017.

[4] J. Han, M. Takenaka, and S. Takagi, “Study on void reduction in direct wafer bonding using Al2O3/HfO2 bonding interface for high-performance Si high-k MOS optical modulators,” Jpn. J. Appl. Phys., Vol. 55, 04EC06, 2016.

Ge受光器

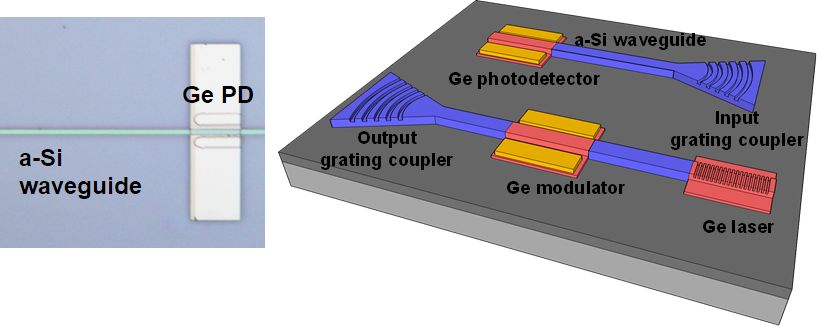

Siフォトニクス・プラットフォーム上に集積可能なGe受光器の研究を進めています。Ge受光器はInGaAs受光器と比較して暗電流が非常に大きいことが問題となっていました。。我々は、気相ドーピング[1]により良好なn+/p接合を形成することで、イオン注入法で作製した場合と比較して、1桁〜2桁程度暗電流が低減可能であることを明らかにしました。さらにGe表面を熱酸化で形成したGeO2でパッシベーションすることで表面リーク電流も低減可能であることを初めて明らかにするなど、世界最小レベルの暗電流密度を実現することに成功しました[2, 3]。ウェハーボンディングによりGe層をSi基板上に貼り合せた導波路型Ge受光器の研究も進めています。貼り合わせで作製したGe-on-Insulator (GeOI)基板上に作製したGe受光器とアモルファスSi(a-Si)導波路を突き合わせ接続した導波路型Ge受光器の実証に成功しています[4]。GeOI基板を用いたGe/a-Siハイブリッドプラットフォームを提唱し、Ge受光器のみならずGe/GeSnレーザーやGe変調器も集積した光集積回路の実現に向けた研究に取り組んでいます。

Ultra-low dark current Ge PD

Ge/a-Si hybird platform

[1] M. Takenaka, K. Morii, M. Sugiyama, Y. Nakano, and S. Takagi, Jpn. J. Appl. Phys., Vol. 50, 010105, 2011.

[2] M. Takenaka, K. Morii, M. Sugiyama, Y. Nakano, and S. Takagi, Optics Express Letters, vol. 20, no. 8, pp. 8718-8725, 2012.

[3] J. Kang, R. Zhang, M. Takenaka, and S. Takagi, "Suppression of dark current in GeOx-passivated germanium metal-semiconductor-metal photodetector by plasma post-oxidation," Optics Express, vol. 23, no. 13, pp. 16967-16976, 2015.

[4] J. Kang, M. Takenaka, and S. Takagi, “Ge waveguide photodetector on wafer-bonded Ge-on-insulator substrate monolithically integrated with amorphous Si waveguide,” European Conference on Optical Communication (ECOC 2016), Düsseldorf, W3.F.2, 21 September 2016.

III-V CMOSフォトニクス

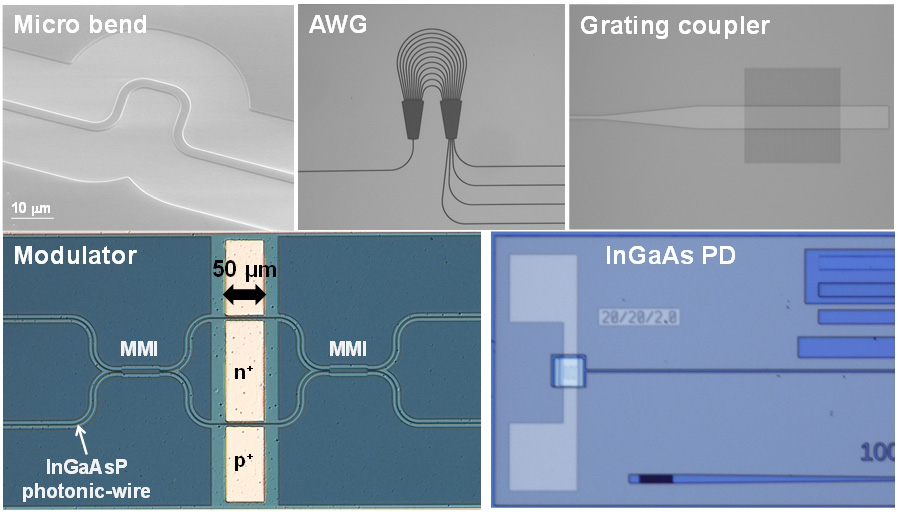

Siよりも光物性に優れた直接遷移型半導体であるIII-V族半導体をSi上に貼り合わせたIII-V CMOSフォトニクスを世界で先駆けて提案して研究を進めています[1, 2]。Siフォトニクスで用いられているSi-on-Insulator基板と同等の構造を持ったIII-V-on-Insulator(III-V-OI)基板を用いることで、強い光閉じ込めをもつ細線導波路を実現可能となり、既存のIII-V族半導体光デバイスを1/100程度の小型化可能になります。いわばIII-V族半導体Siフォトニクスを実現することで、Siフォトニクスを凌駕する光電子集積回路の実現を目指しています。ウェハーボンディング技術を用いて、熱酸化Si基板上にInGaAsP層を貼り合せたIII-V-OI構造を世界に先駆けて実現しました[3]。この貼り合わせIII-V-OI基板を用いることで、従来のInP光素子で不可能だった超小型曲げ導波路や波長分波器[3]、グレーティングカプラ[4]の動作実証に成功しました。さらに電流注入を用いた光変調器/スイッチ[4, 5]、導波路型InGaAs受光器[6-8]などの実証に成功しています。CMOS技術を駆使して、III-V CMOSフォトニクス・プラットフォーム上にレーザー、光変調器、受光器、化合物トランジスタをモノリシック集積した光電子集積回路の実現を目指した研究を進めています。

III-V CMOS photonics platform

Active and passive devices on III-V CMOS photonics platform

[1] M. Takenaka and Y. Nakano, Optics Express Letters, vol. 15, no. 13, pp. 8422-8427, 2007.

[2] M. Takenaka, M. Yokoyama, M. Sugiyama, Y. Nakano, and S. Takagi, Optical Fiber Communication Conference (OFC’10), OThS5, San Diego, March 2010.

[3] M. Takenaka, M. Yokoyama, M. Sugiyama, Y. Nakano, and S. Takagi, Appl. Phys. Express., Vol. 2, 122201, 2009.

[4] Y. Ikku, M. Yokoyama, O. Ichikawa, M. Hata, M. Takenaka, and S. Takagi, Optics Express Letters, vol. 20, no. 26, pp. B357-B364, 2012.

[5] J.-K. Park, J. Han, M. Takenaka, and S. Takagi, “InGaAsP variable optical attenuator with lateral P-I-N junction formed by Ni-InGaAsP and Zn diffusion on III-V on insulator wafer,” MRS Advances, vol.1 no. 48, pp. 3295-3300, 2016. [6] Y. Cheng, Y. Ikku, M. Takenaka, and S. Takagi, IEICE Electronics Express, vol. 11, no. 16, pp. 20140609, 2014.

[7] Y. Cheng, Y. Ikku, M. Takenaka, and S. Takagi, “Surface leakage reduction in MSM InGaAs photodetector on III–V CMOS photonics platform,” IEEE Photonics Technology Letters, Vol. 27, No. 14, pp. 1569-1572, 2015.

[8] Y. Cheng, Y. Ikku, M. Takenaka, and S. Takagi, “Low-dark-current waveguide InGaAs metal–semiconductor–metal photodetector monolithically integrated with InP grating coupler on III–V CMOS photonics platform,” Jpn. J. Appl. Phys., Vol. 55, 04EH01, 2016.

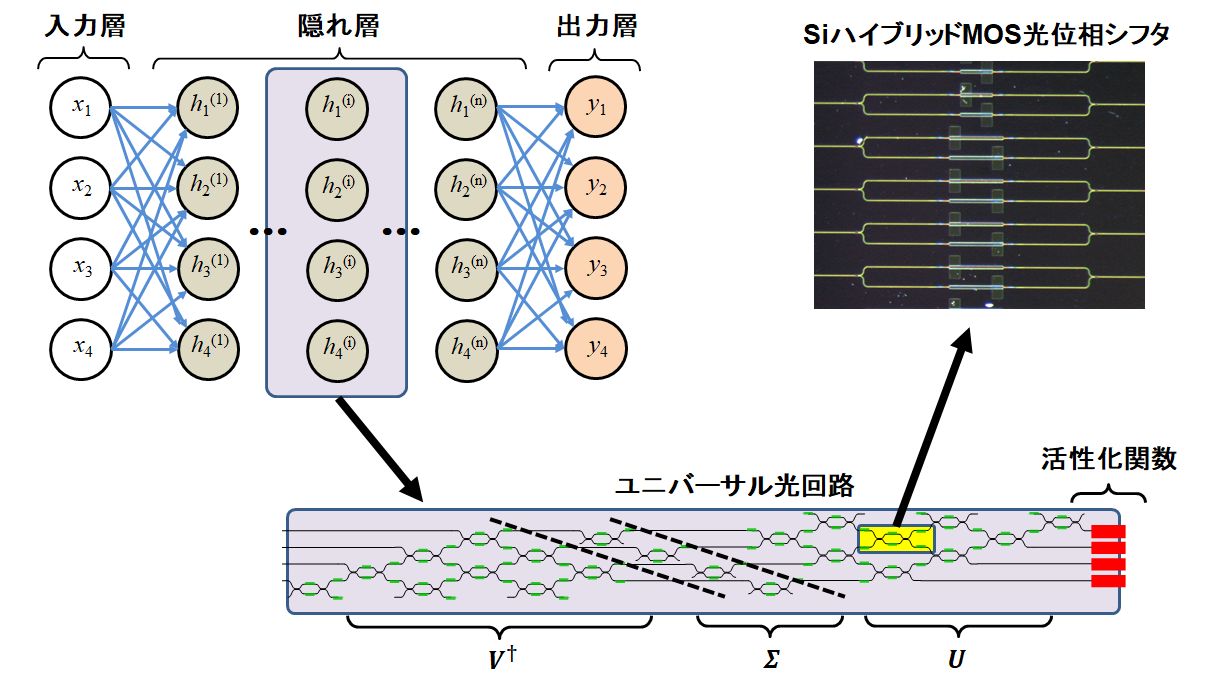

ユニバーサル光回路を用いた深層学習

Siフォトニクス技術の進展により大規模光集積回路な可能になり、多数の光スイッチを網目状に集積して任意の線形操作を可能とするユニバーサル光回路に注目が集まっています。光通信用の様々な機能を実現できるだけでなく、光レーダー(LiDAR)や光ニューラルネットワークを用いた深層学習、量子コンピューターなどの応用が期待されることから、活発な研究が世界中で進められています。ユニバーサル光回路を実現するためには、高性能な光位相シフタが必要となります。我々は、世界に先駆けてIII-V/SiハイブリッドMOS光位相シフタの実証に成功しました[1]。従来の熱光学効果を用いた光位相シフタと比べて、動作速度は1000倍、消費電力は100万分の1になることから、ユニバーサル光回路の性能を飛躍的に高めることが出来ると期待されています[2]。現在、SiハイブリッドMOS光位相シフタを用いたユニバーサル光回路を使った深層学習などの機械学習を実現するための研究に取り組んでいます[3]。

Deep learning using universal photonic integrated circuits with III-V/Si hybrid MOS optical phase shifters

[1] J.-H. Han, F. Boeuf, J. Fujikata, S. Takahashi, S. Takagi, and M. Takenaka, “Efficient low-loss InGaAsP/Si hybrid MOS optical modulator,” Nature Photonics, vol. 11, no. 8, pp. 486–490, Jul. 2017.

[2] Q. Li, J.-H. Han, C. Ho, S. Takagi, and M. Takenaka, “Low-crosstalk, low-power Mach-Zehnder interferometer optical switch based on III-V/Si hybrid MOS phase shifter,” Optical Fiber Communication Conference (OFC2018), Th3C.5, San Diego, 15 March 2018.

[3] M. Takenaka, J.-H. Han, J.-K. Park, F. Boeuf, J. Fujikata, S. Takahashi, and S. Takagi, “High-efficiency, low-loss optical phase modulator based on III-V/Si hybrid MOS capacitor,” Optical Fiber Communication Conference (OFC2018), March 2018 (invited).

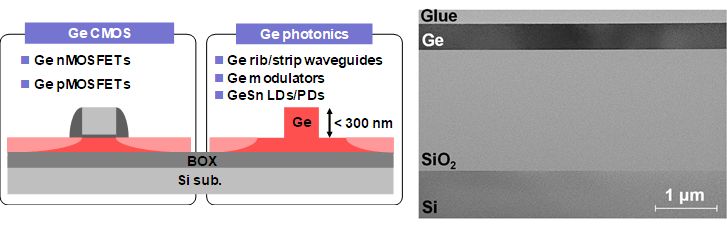

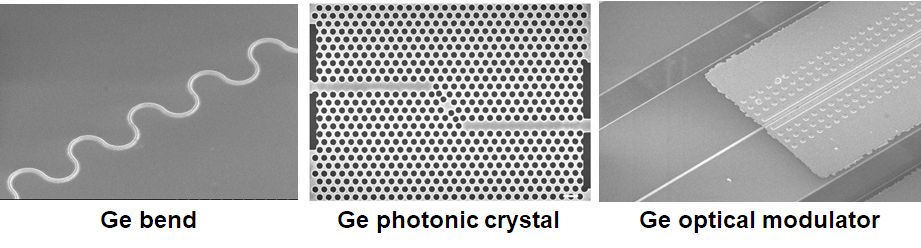

中赤外光集積回路

近年、波長2umから15um程度の中赤外光を用いた光集積回路が注目を集めています。光ファイバー・空間通信に加えて、分子振動に応じた固有の光吸収を用いた医療・バイオセンサー、ガスセンサー、食品センサー、環境モニターなど幅広い光センシング応用が期待されています。光ファイバー通信で用いられている近赤外光と比較して、中赤外光はこれまで十分活用されていませんでしたが、Siフォトニクス技術の進展により、中赤外でも動作する光集積回路を実現する機運が高まっています。しかし、既存のSiフォトニクスではSi自体の吸収により波長7um程度までしか中赤外光を活用できないことが問題となっていました。我々は、中赤外光全域で透明なGeを用いた中赤外光集積回路の研究に取り組んでいます。Ge-on-Insulator (GeOI)基板上に中赤外全域で動作するGe光回路とGe CMOSをモノリシック集積可能なGe CMOSフォトニクスを提唱して、研究を進めています[1-4]。ウェハボンディングを用いて極めて高品質なGeOI基板の実現に成功し、急峻な曲げ導波路や各種パッシブ中赤外導波路の実証に成功しています。またキャリア注入を用いた中赤外Ge光変調器の動作にも世界で初めて成功しました。現在、中赤外光センシングや中赤外光通信の実現に向けた光集積回路技術の研究に取り組んでおり、新たな中赤外光応用の開拓を目指します。

Ge CMOS photonics platform

Ge active and passive devices

[1] J. Kang, X. Yu, M. Takenaka and S. Takagi, “Impact of thermal annealing on Ge-on-Insulator substrate fabricated by wafer bonding,” Materials Science in Semiconductor Processing, vol. 42, Part 2, pp. 259-263, 2016.

[2] J. Kang, M. Takenaka, and S. Takagi, “Novel Ge waveguide platform on Ge-on-insulator wafer for mid-infrared photonic integrated circuits,” Optics Express, vol. 24, no. 11, pp. 11855-11864, 2016.

[3] J. Kang, Z. Cheng, W. Zhou, T.-H. Xiao, K.-L. Gopalakrisna, M. Takenaka, H. K. Tsang, and K. Goda, “Focusing subwavelength grating coupler for mid-infrared suspended membrane germanium waveguides,” Optics Letters, vol. 42, no. 11, pp. 2094 – 2097, 2017.

[4] T. H. Xiao, Z. Zhao, W. Zhou, M. Takenaka, H. K. Tsang, Z. Cheng, and K. Goda, “Mid-infrared germanium photonic crystal cavity,” Optics Letters, vol. 42, no. 15, pp. 2882 – 2885, 2017.

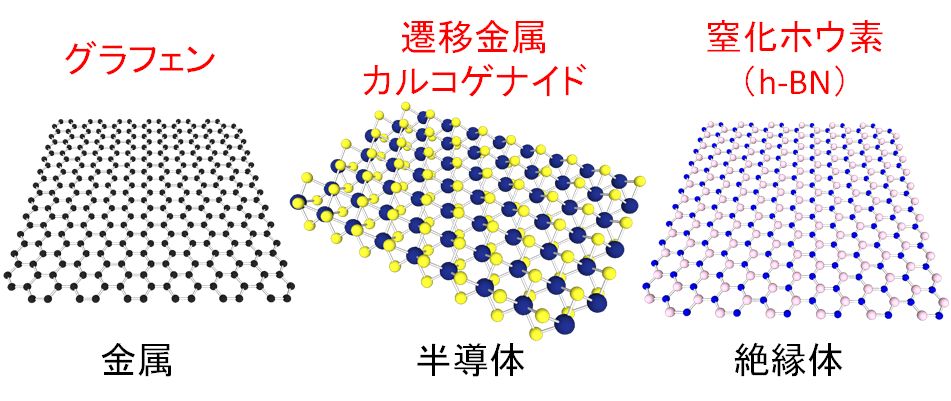

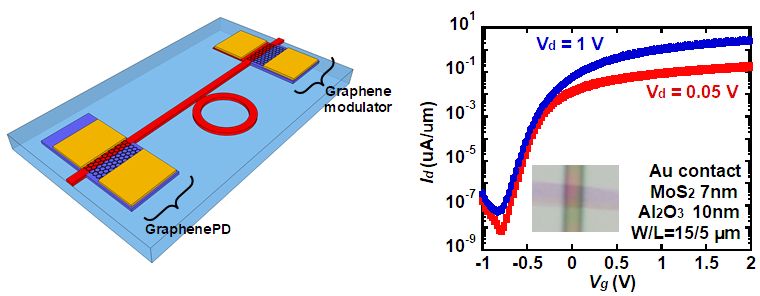

2次元材料デバイス

近年、原子層状の物質である2次元材料に注目が集まっており、特異な物性を活かした種々の新しいデバイスの研究が活発に行われています。金属的な振る舞いをするグラフェンだけでなく、半導体として機能する二硫化モリブデンなどの遷移金属カルコゲナイド、絶縁膜となる窒化ホウ素などを組み合わせたトランジスタや光素子など高性能集積回路やフレキシブル集積回路への応用が期待されています。当研究室でも、グラフェンを使った光変調器・受光器[1, 2]や二硫化モリブデン(MoS2)を使ったMOSFET[3]の研究を進めています。

2D materials

Graphene based photonic devices and MoS2 MOSFET

[1] T. Kayoda, J. Han, M. Takenaka and S. Takagi, "Evaluation of Chemical potential for graphene optical modulators based on the semiconductor-metal transition," International Conference on Group IV Photonics (GFP2013), ThD5, Seoul, 29 August 2013.

[2] Y. Yamaguchi, S. Takagi, and M. Takenaka, “Low-optical-loss graphene-based phase modulator operating at mid-infrared wavelength,” International Conference on Solid State Devices and Materials (SSDM2017), PS-7-03, Sendai, 19-22 September 2017.

[3] M. Takenaka, Y. Ozawa, J. Han, and S. Takagi, “Quantitative evaluation of energy distribution of interface trap density at MoS2 MOS interfaces by the Terman method,” International Electron Devices Meeting (IEDM’16), 5.8, San Francisco, 5 December 2016.